I lead the Energy Efficient Circuits and Systems Group at the German University in Cairo. Currently , the internet of things (IoT) is driving a new computing era by enabling the wireless connectivity of nearly everything we use. Vehicles, appliances, civil-engineering structures, manufacturing equipment, livestock and even our own bodies will have embedded sensors that report information directly to networked servers, aiding with maintenance and the coordination of tasks. The creativity in this new era of the IoT is boundless, with amazing potential to immensely improve human life. Realizing that vision, however, will require extremely low-power sensing systems that can run for months without battery changes - or, even better, that can extract energy from the environment to recharge. Moreover, the flexibility and the miniaturization of such systems are highly desirable to ease their integration with various structures. Thus, the future growth of the IoT will be contingent upon innovations in ultra-low power circuit design techniques, system architecture, as well as novel material technologies. In my research work, I explore efficient means of scavenging and managing energy from our surroundings to allow the autonomous operation of ultra-low power systems. I work on integrated circuits and systems design, ultra-low power electronics for heavily duty-cycled applications. I also have a particular interest in blending emerging materials with silicon CMOS technology to push the boundaries of today’s electronics.

GUC B.Sc. Project Student

- Mohamed Gamal Hemdan, Topic: High Efficiency Power Management Circuits

Below is a brief about part of the published work that I have conducted in the Energy-Efficient Circuits and Systems Group at MIT under the supervision of Prof. Anantha Chandrakasan.

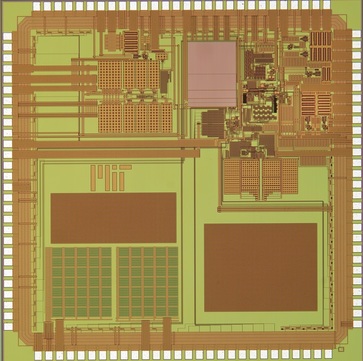

A 10nW-1μW Power Management IC with Integrated Battery Management and Self-startup for Energy Harvesting Applications

A solar energy harvesting chip with 3.2nW quiescent power. The chip integrates self-startup, battery management, supplies 1V regulated rail with single inductor and supports power range of 10nW to 1μW. The control circuit is designed in an asynchronous fashion that scales the effective switching frequency of the converter with the level of the power transferred. The on-time of the converter switches adapts dynamically to the input and output voltages for peak-current control and zero-current switching. For input power of 500nW, the proposed system achieves an efficiency of 82%, including the control circuit overhead, while charging a battery at 3V from 0.5V input. In buck mode, it achieves a peak efficiency of 87% and maintains efficiency greater than 80% for output power of 50nW-1μW with input voltage of 3V and output voltage of 1V.

Publications:

[JSSC 2016] D. El-Damak, A. Chandrakasan, “A 10nW-1μW Power Management IC with Integrated Battery Management and Self-startup for Energy Harvesting Applications,” IEEE Journal of Solid-State Circuits (JSSC), vol. 51, no. 4, pp. 943-954, April 2016.

[VLSI 2015] D. El-Damak and A. P. Chandrakasan, “Solar Energy Harvesting System with Integrated Battery Management and Startup Using Single Inductor and 3.2nW Quiescent Power,” IEEE Symposium on VLSI Circuits (VLSIC), Kyoto, Japan, June 2015.

Press:

MIT News Office: Toward tiny, solar-powered sensorsNew ultralow-power circuit improves efficiency of energy harvesting to more than 80 percent. [Featured on MIT Home Page]

CNBC: Big step toward solar power for small electronic devices

Solar Novus: Ultra-low-power Converter Chip for Tiny Solar-Powered Sensors

QMED: New Ultra-Low Power Sensors Can Self Charge

Publications:

[JSSC 2016] D. El-Damak, A. Chandrakasan, “A 10nW-1μW Power Management IC with Integrated Battery Management and Self-startup for Energy Harvesting Applications,” IEEE Journal of Solid-State Circuits (JSSC), vol. 51, no. 4, pp. 943-954, April 2016.

[VLSI 2015] D. El-Damak and A. P. Chandrakasan, “Solar Energy Harvesting System with Integrated Battery Management and Startup Using Single Inductor and 3.2nW Quiescent Power,” IEEE Symposium on VLSI Circuits (VLSIC), Kyoto, Japan, June 2015.

Press:

MIT News Office: Toward tiny, solar-powered sensorsNew ultralow-power circuit improves efficiency of energy harvesting to more than 80 percent. [Featured on MIT Home Page]

CNBC: Big step toward solar power for small electronic devices

Solar Novus: Ultra-low-power Converter Chip for Tiny Solar-Powered Sensors

QMED: New Ultra-Low Power Sensors Can Self Charge

Flexible Circuit Design using 2D Materials

In collaboration with Lili Yu, Sungjae Ha and Prof. Tomas Palacios

In collaboration with Lili Yu, Sungjae Ha and Prof. Tomas Palacios

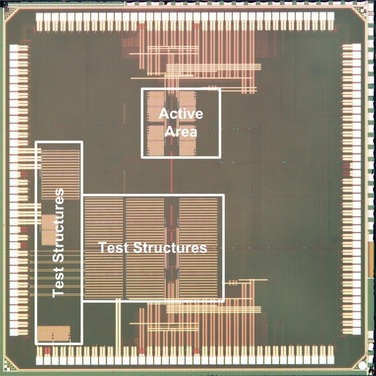

This project is focused on the design of large-scale electronics using Molybdenum disulfide (MoS2), one of the emerging 2D materials. In the first phase of the project we developed a computer-aided design (CAD) flow for MoS2 based circuits. The work encompassed device modeling in Verilog-A, building custom technology library for the layout of MoS2 devices, along with circuit design and testing, which paves the road for the realization of large-scale flexible MoS2 systems. We validated the flow with the design, fabrication and testing of multiple circuit blocks.

Publications:

[Nano Letters] L. Yu*, D. El-Damak*, U. Radhakrishna, X. Ling, A. Zubair, Y. Lin, Y. Zhang, M. Chuang, Y-H. Lee, D. Antoniadis, J. Kong, A. Chandrakasan, T. Palacios, "Design, Modeling, and Fabrication of Chemical Vapor Deposition Grown MoS2 Circuits with E-mode FETs for Large-Area Electronics" Nano Letters 2016 16 (10), 6349-6356.

[IEDM 2015] L. Yu, D. El-Damak, S. Ha, X. Ling, Y. Lin, A. Zubair, Y.-H. Lee, J. Kong, A. Chandrakasan, T. Palacios, “Enhancement-Mode Single-layer CVD MoS2 FET Technology for Digital Electronics,” IEEE International Electron Devices Meeting (IEDM), Washington, D.C., Dec. 2015.

[VLSI 2015] L. Yu, D. El-Damak, S. Ha, S. Rakheja, X. Ling, D. Antoniadis, Jing Kong, A. Chandrakasan, and T. Palacios, “MoS2 FET Fabrication and Modeling for Large-Scale Flexible Electronics,” IEEE Symposium on VLSI Technology (VLSIT), Kyoto, Japan, June 2015.

* Authors Contributed Equally to the work.

Press:

Compound Semiconductor: The promise of truly two-dimensional transistors

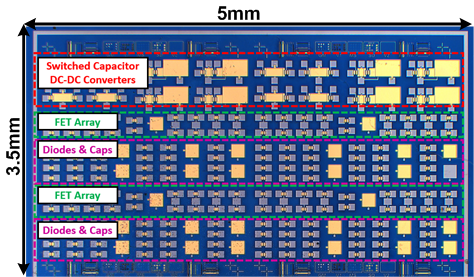

Reconfigurable Switched Capacitor DC-DC Converter using On-Chip Ferroelectric Capacitors

A re-configurable switched capacitor DC-DC converter featuring high density ferroelectric capacitors (Fe-Caps) for charge transfer was designed in this work. The converter supports four gain settings (1-2/3-1/2-1/3) to supply wide output voltage range and is split in four modules for output voltage ripple reduction. The control circuit exploits dynamic gain selection and Pulse Frequency Modulation (PFM) for efficient output voltage regulation of the multi-phased converter. The chip was fabricated in 130 nm CMOS process. It supports output voltage of 0.4V to 1.1V from 1.5V input while delivering load current of 20µA to 1mA and achieves a peak efficiency of 93% including the control circuit overhead.

Publications:

[ISSCC 2013] D. El-Damak, S. Bandyopadhyay, A. P. Chandrakasan, “A 93% Efficiency Reconfigurable Switched-Capacitor DC-DC Converter Using On-Chip Ferroelectric Capacitors,” IEEE International Solid-State Circuits Conf. (ISSCC), San Francisco, CA, pp. 374-375, Feb. 2013.

Press:

Electronics Weekly: Power is king at ISSCC this year

ISSCC 2013 Tech Trends

Publications:

[ISSCC 2013] D. El-Damak, S. Bandyopadhyay, A. P. Chandrakasan, “A 93% Efficiency Reconfigurable Switched-Capacitor DC-DC Converter Using On-Chip Ferroelectric Capacitors,” IEEE International Solid-State Circuits Conf. (ISSCC), San Francisco, CA, pp. 374-375, Feb. 2013.

Press:

Electronics Weekly: Power is king at ISSCC this year

ISSCC 2013 Tech Trends

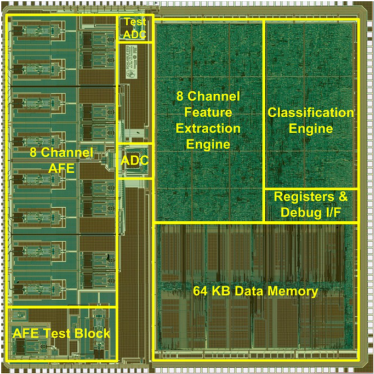

Ultra-low Power ADC for EEG Acquisition SoC

In Collaboration with Prof. Jerald Yoo, Long Yan

In Collaboration with Prof. Jerald Yoo, Long Yan

This project focused on the design of an 8-channel scalable EEG acquisition SoC to continuously detect and record patient-specific seizure onset activities from scalp EEG. The SoC integrated 8 high-dynamic range Analog Front-End (AFE) channels, ADC, a machine-learning seizure classification processor and a 64KB SRAM. I was responsible mainly for the design of the ADC. A differential capacitive DAC was utilized to enhance the ADC CMRR as well as both concepts of split-capacitor array and sub-DAC to reduce the DAC area and power consumption. The ADC core consumes 1 uW from 1 V supply at a sampling rate of 32 kHz and has a maximum DNL and INL of 0.55 LSB and 0.75 LSB respectively.

Publications:

[JSSC 2013] J. Yoo, L. Yan, D. El-Damak, M. Bin Altaf, A. Shoeb, and A. P. Chandrakasan, “An 8-channel Scalable EEG Acquisition SoC with Patient-Specific Seizure Classification and Recording Processor,” IEEE Journal of Solid-State Circuits (JSSC), vol.48, no.1, pp. 214 - 228, Jan. 2013.

[ISSCC 2012] J. Yoo, L. Yan, D. El-Damak, M. Bin Altaf, A. Shoeb, H-J. Yoo , A. Chandrakasan “An 8-Channel Scalable EEG Acquisition SoC with Fully Integrated Patient-Specific Seizure Classification and Recording Processor,” IEEE International Solid-State Circuits Conf. (ISSCC), San Francisco, CA, pp. 292-294, Feb. 2012.

Patents:

J. Yoo, A. P. Chandrakasan , L. Yan, D. El-Damak, A. Shoeb, and M. Bin Altaf, "Multi-channel Scalable EEG Acquisition System on a Chip with Integrated Patient Specific Seizure Classification and Recording Processor," US Patent App. 14/378,833, 2013.

Press:

EETimes : ISSCC highlights sensors and semiconductor technology in medicine

Publications:

[JSSC 2013] J. Yoo, L. Yan, D. El-Damak, M. Bin Altaf, A. Shoeb, and A. P. Chandrakasan, “An 8-channel Scalable EEG Acquisition SoC with Patient-Specific Seizure Classification and Recording Processor,” IEEE Journal of Solid-State Circuits (JSSC), vol.48, no.1, pp. 214 - 228, Jan. 2013.

[ISSCC 2012] J. Yoo, L. Yan, D. El-Damak, M. Bin Altaf, A. Shoeb, H-J. Yoo , A. Chandrakasan “An 8-Channel Scalable EEG Acquisition SoC with Fully Integrated Patient-Specific Seizure Classification and Recording Processor,” IEEE International Solid-State Circuits Conf. (ISSCC), San Francisco, CA, pp. 292-294, Feb. 2012.

Patents:

J. Yoo, A. P. Chandrakasan , L. Yan, D. El-Damak, A. Shoeb, and M. Bin Altaf, "Multi-channel Scalable EEG Acquisition System on a Chip with Integrated Patient Specific Seizure Classification and Recording Processor," US Patent App. 14/378,833, 2013.

Press:

EETimes : ISSCC highlights sensors and semiconductor technology in medicine